Fhss Transmitter And Receiver Block Diagram. In slow hopped FHSS hopping is done at the rate slower than information bit rate. Figure 1 - Signals used to modulate the carrier in FHSS and DSSS Dwell time in FHSS is represented as 3 x data bit duration. Due to support of wide bandwidth. Home Uncategorized Fhss Transmitter And Receiver Block Diagram.

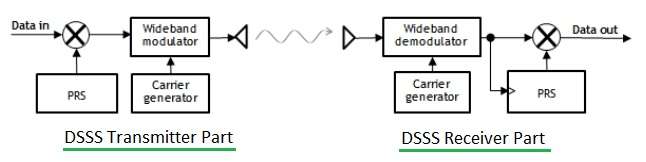

The block diagram has the message S t passing through a block labeled transmitter that produces the signal X t. Using this transmission code we can synchronize the receiver with transmitter at any instant of time. Spreading sequence in DSSS is represented as being 5 chip long Notes. Timestamp field gives transmitter clock value. Due to support of wide bandwidth. This system can be represented by the following block diagram shown in Figure 1.

Due to support of wide bandwidth.

Spreading sequence in DSSS is represented as being 5 chip long Notes. The receiver block diagram is shown in Fig. The gate level model is analysed and then by using Matlab simulink the FHSS Transceiver design will be carried. The FHSS signal doesnt stay in one place on the band FHSS can elude a jammer a transmitter designed to block radio transmissions on a given frequency. From my analyses of the R3008SB and SF800 S-FHSS receivers I expect the receiver noise figure to be around 4 dB 05 dB for each of two switches 2 dB for the LNA 1 dB for circuit losses. Goreng 24 Dec 2018 0 Mt 305 3ch 24 Ghz Fhss Radio Control System User Manual Out アナログ振幅変復調について Dsb Scssb Sc変復調 サーキット Fhss.